quartus ii 9.0安装包-QuartusII 9.0免费版下载 附安装教程和注册码

quartus ii 9.0是由Altera公司开发的一款综合性的CPLD/FPGA开发软件,软件集成了与电路结构相关的开发包环境,知识兔包括原理图绘制、结构框图绘制和电路描述等功能,还可进行嵌入式的逻辑分析、延时分析和仿真分析等。quartus ii 9.0是一个非常经典且稳定的版本,知识兔小编这里找出来供大家下载,破解版附有注册码,安装之后可免费使用。

quartus ii 9.0安装破解教程

1.解压下载的软件,得到安装文件和破解文件

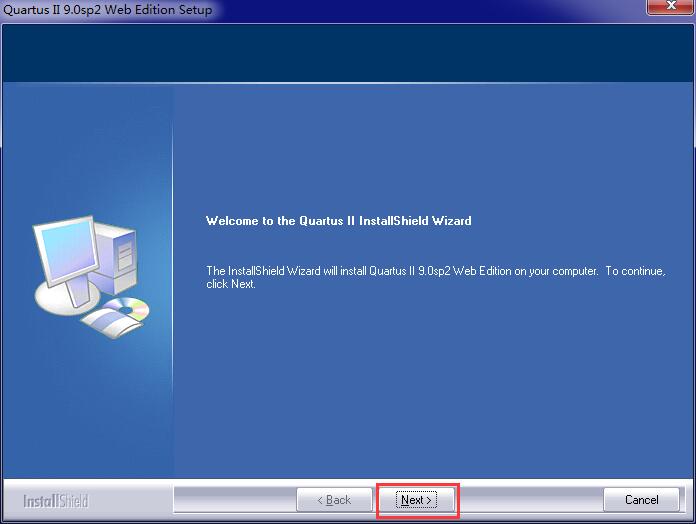

2.运行setup.exe,进入欢迎安装界面,单击【next】

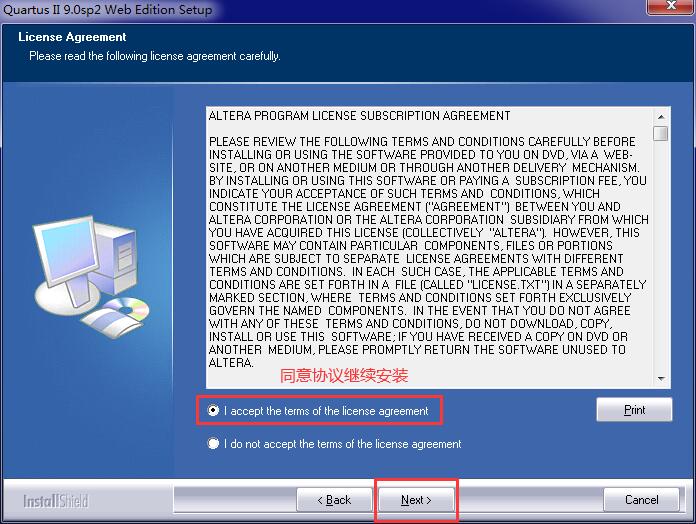

3.阅读软件的许可协议,勾选【I accept…】表示同意协议继续安装

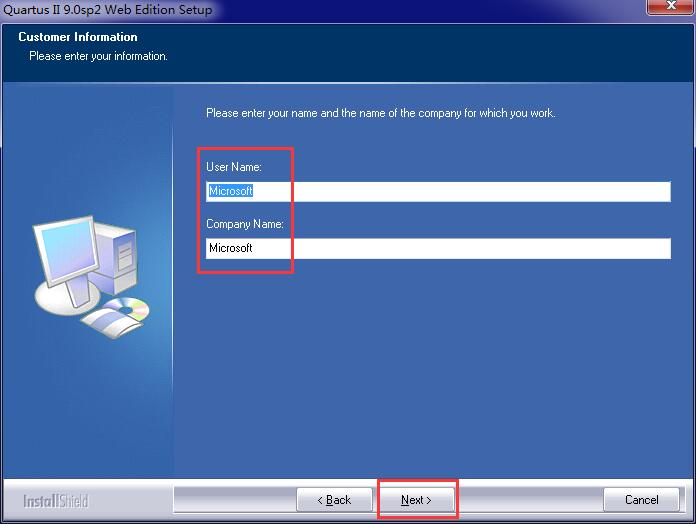

4.输入用户信息

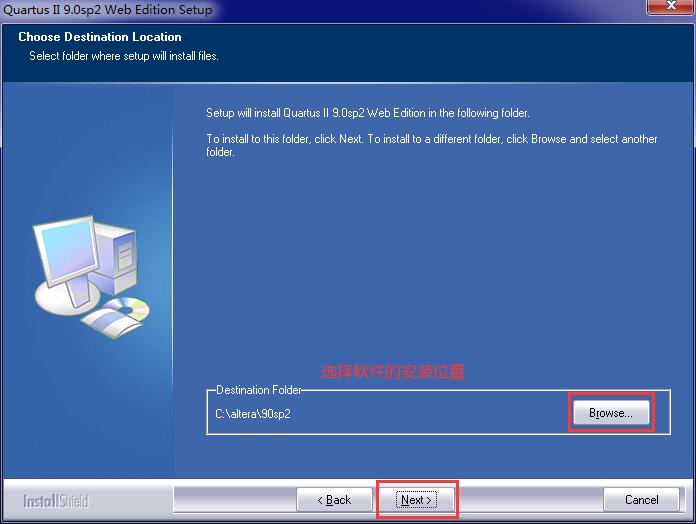

5.选择软件的安装目的地,默认的是【C:\altera\90sp2】,单击【browse】自定义

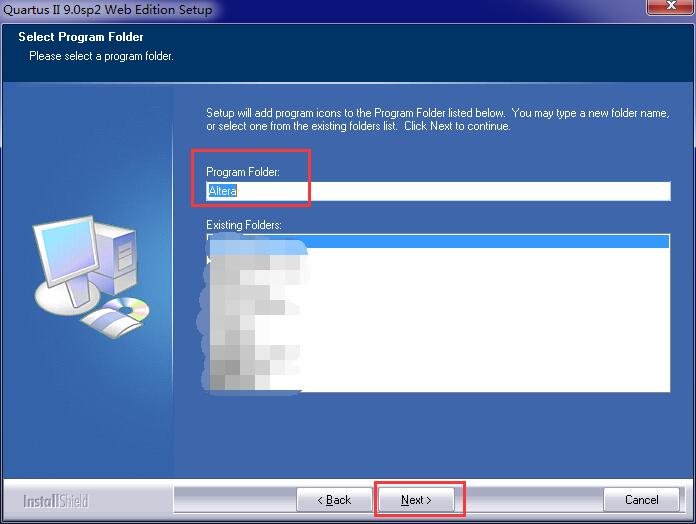

6.选择开始菜单文件夹

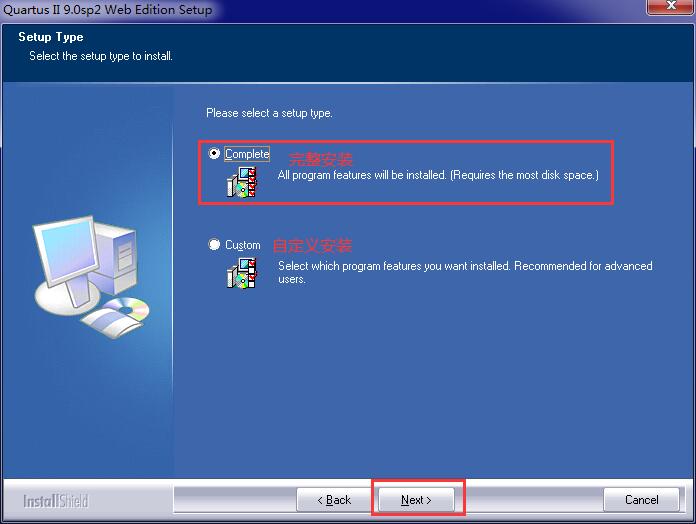

7.选择安装类型,知识兔包括完整安装和自定义安装两种,知识兔根据自己的需要选择,知识兔默认【complete】完整安装

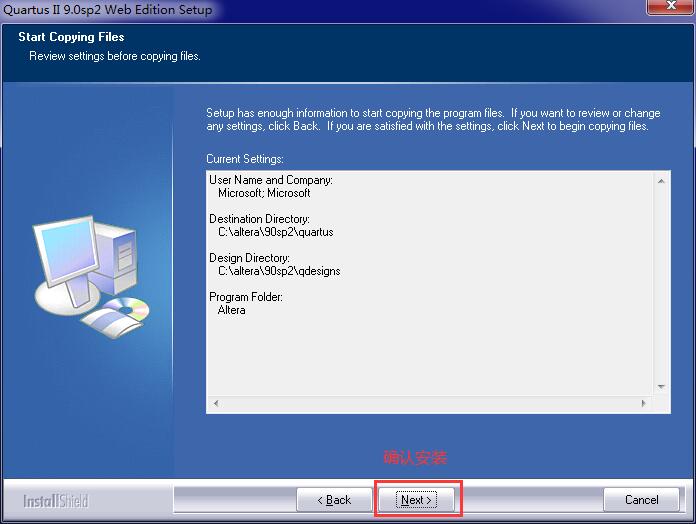

8.确认安装信息,单击【next】开始安装

9.知识兔打开软件,知识兔点击Tools-License Setup;

10.复制NIC ID,暂时先不关闭此界面;

11.以记事本方式打开破解文件夹中的license.DAT,再将刚刚复制的ID粘贴进去;

12.在将修改好的license.DAT文件复制到软件安装目录下;

默认目录【C:\altera\90sp2】

13.回到第10步骤中的界面,知识兔点击三个点改成知识兔刚刚放置License的路径;

14.最后将破解文件夹中bin32目录下的sys_cpt.dll复制到安装目录下进行替换;

默认目录【C:\altera\90sp2\quartus\bin】

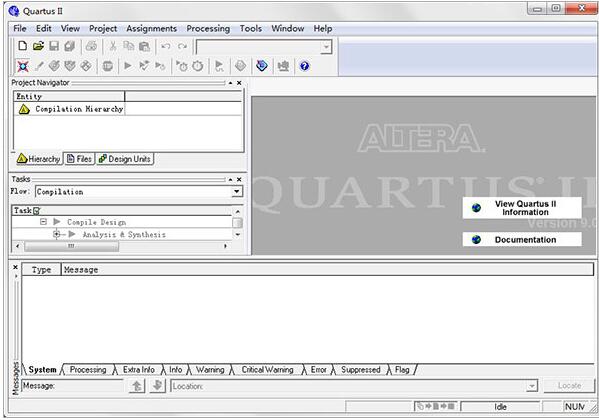

15.顺利完成破解,知识兔打开即可免费使用

软件特色

-可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件

-芯片(电路)平面布局连线编辑

-LogicLock增量设计方法,用户可建立并优化系统,然后知识兔添加对原始系统的性能影响较小或无影响的后续模块

-功能强大的逻辑综合工具

-完备的电路功能仿真与时序逻辑仿真工具

-定时/时序分析与关键路径延时分析

-可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析

-支持软件源文件的添加和创建,并将它们链接起来生成编程文件

-使用组合编译方式可一次完成整体设计流程

-自动定位编译错误

-高效的期间编程与验证工具

-可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件

-能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件

使用教程

例程测试

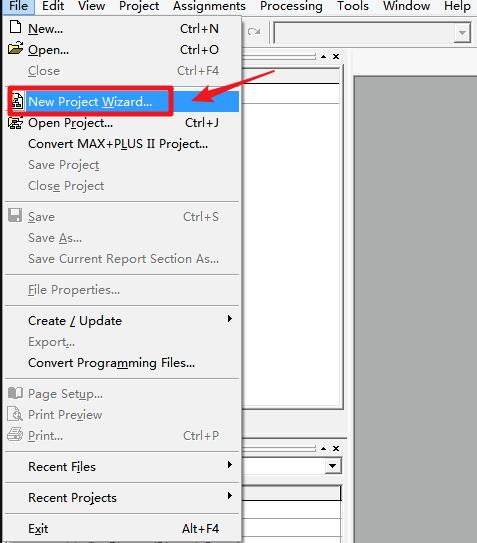

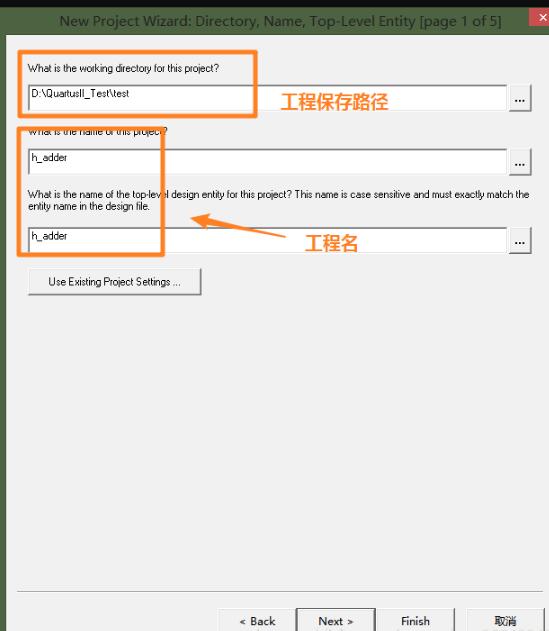

1.使用向导新建一个工程,File->New Project Wizard

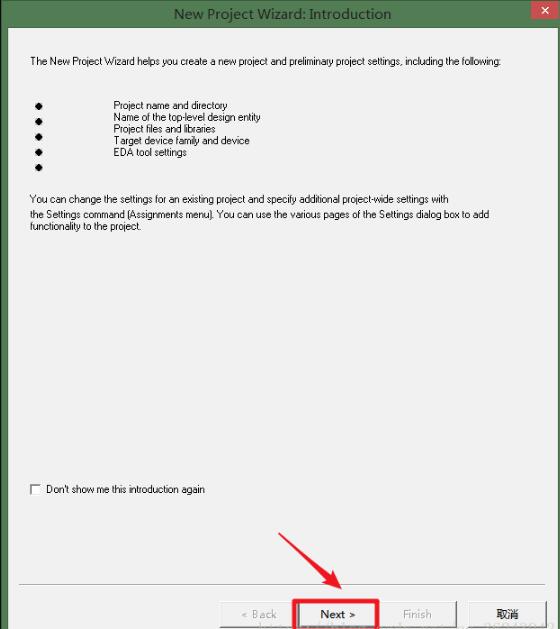

2.下一步

3.选择保存路径:

4.添加设计文件到您的工程目录下面,如果知识兔没有设计文件,则知识兔点击”NEXT”

5.选择器件的具体型号:

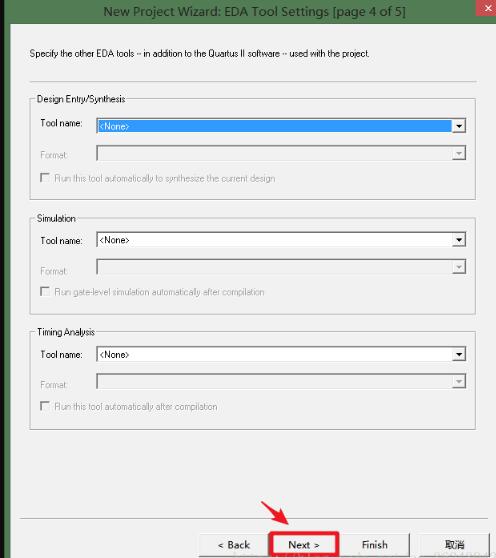

6.选择设计综合工具,知识兔选择仿真工具,知识兔选择时序分析工具,默认,就知识兔点击”NEXT”

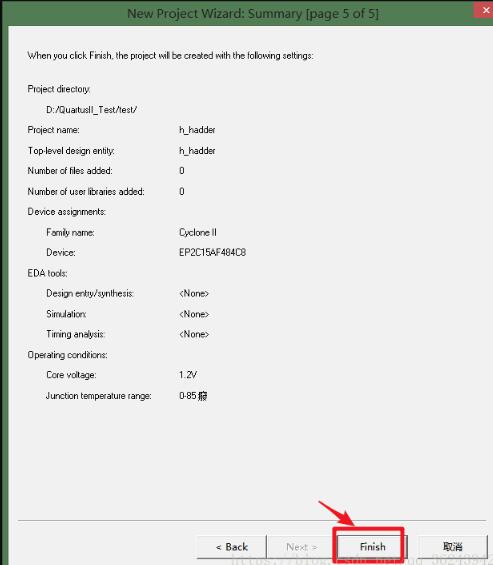

7.知识兔点击”FINISH”,工程文件建立成功

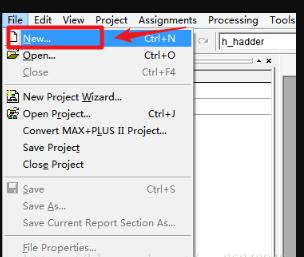

8.新建设计文件,知识兔点击”FILE”—–“NEW”

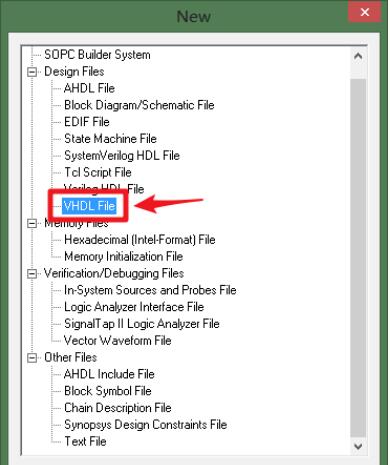

9.选择”VHDL File”:

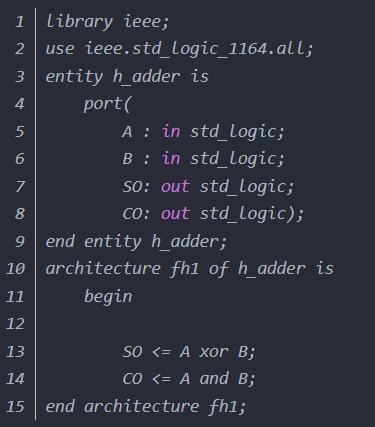

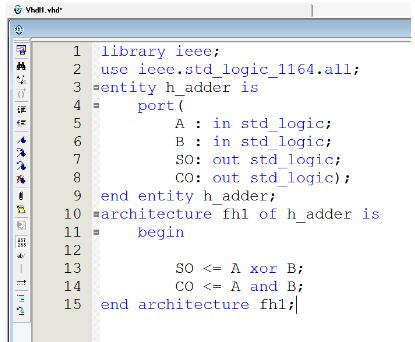

10.编写一个简单的半加器实验:

具体代码如下:

把这段代码粘贴到新建的file中:

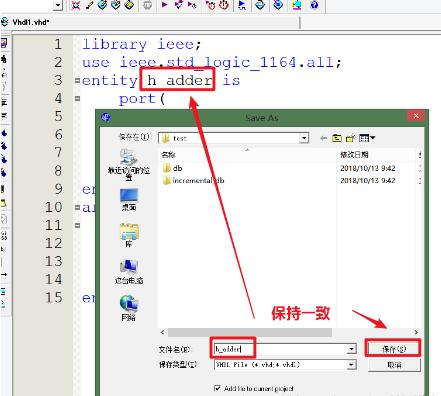

11.知识兔点击保存后,必须注意一点,您所设计的模块名,必须和您保存的文件名字完全相同

12.知识兔点击开始编译

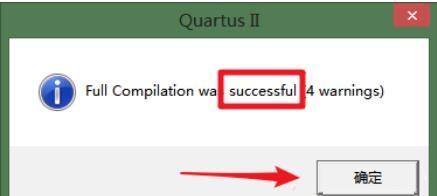

13.编译成功,弹出对话框,确定:

常见问题

一、多功能管脚的设置?

在用FLASH分配完管脚后编译出现如下错误:

Error: Can鈥檛 place multiple pins assigned to pin location Pin_108 (IOC_X34_Y2_N0)

nfo: Fitter preparation operations ending: elapsed time is 00:00:00

Error: Can鈥榯 fit design in device

Error: Quartus II Fitter was unsuccessful. 2 errors, 0 warnings

Error: Quartus II Full Compilation was unsuccessful. 4 errors, 56 warnings

原因是不能分配给多功能管脚PIN_108。

这是由于PIN_108是一个多功能管脚,还有一个功能是nCEO,也是默认的功能。如果知识兔要用它当普通IO,需要提前设置一下:assignments》device》device and pin options》dual-purpose pins里面把nCEO设置成use as regular i/o就可以了。

二、仿真时存储器初始化?

在使用FPGA内部的RAM时,会有一个初始化文件.mif,给RAM加上初始值或当作ROM用,因此仿真时必须把相应数据导入,首先要把mif文件转换为.hex文件或.rif文件。

在Quartus II环境下,知识兔打开mif文件,点Save As,知识兔选择Hexadecimal(Intel-Format) File(*.hex),或者知识兔点击Export,用Save as type选择RAM Initialization File (*.rif),也可能在命令行下输入:

mif2rif

打开ram模块文件,找到lpm_file或init_file,指向刚刚生成的hex文件或rif文件。

lpm_ram_dp_component.lpm_file = “path

使用hex文件时,不需要compiler directives,知识兔使用rif文件时,需要加入USE_RIF,如下

vlog -work alter_mf altera_mf.v +define+USE_RIF=1

这样就完成了数据导入。

三、多模块或多进程驱动同一信号?

Error (10028): Can鈥榯 resolve multiple constant drivers for net “FLASH_A[7]” at led.v(32)

用Verilog描述电路时,一个信号只能在一个进程中驱动,如果知识兔在多个进程中对其驱动的话将产生如上错误。解决方法为可以另加一个信号,通过在另一个进程中监视这个信号做出相应的动作。

下载仅供下载体验和测试学习,不得商用和正当使用。